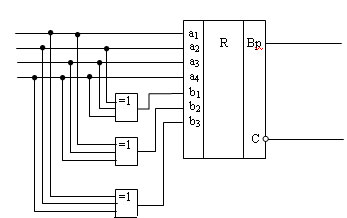

Принципиальная электрическая схема кодера Хэмминга

Принципиальная электрическая схема кодера Хэмминга с поэлементным формированием проверочных элементов кода (7,4) приведена на рисунке 5. Эта схема построена в соответствии с выражениями, полученными в п. 3.6 или в соответствии с проверочной матрицей данного кода записанной в п. 3.8. Кодер включает в себя: сдвигающий регистр, осуществляющий преобразование параллельного кода в последовательный, и логические элементы сложения по модулю два, которые осуществляющие формирование проверочных символов. Количество этих элементов определяется количеством проверочных элементов кодовой комбинации.

Принципиальная электрическая схема декодера Хэмминга

Декодер Хэмминга должен не только произвести проверку на верность принятой комбинации, но и при наличии ошибки должен осуществить ее исправление, поэтому декодер содержит две части: схему определения синдрома и схему исправления ошибки. Кроме того декодер содержит регистр, который служит для преобразования последовательного кода в параллельный. Принципиальная электрическая схема декодера представлена на рисунке 6. Схема определения синдрома кода состоит из логических элементов сложения по модулю два. В них осуществляется определение проверочных символов bi’’ в соответствии с принятыми информационными символами ai’ и проверочной матрицей. В следующих сумматорах по модулю два осуществляется сложение принятых проверочных элементов с полученными на приеме, в результате чего получают синдром кода Сi. Схема исправления ошибки состоит из логических элементов И, в которых формируется сигнал ошибки для ошибочного разряда, и логических элементов сложения по модулю два, в которых и осуществляется исправление ошибочного разряда (его инвертирование). Количество элементов И и сумматоров по модулю два определяется количеством информационных элементов кодовой комбинации, т. к. ошибка в проверочной части не приводит к искажению сообщения и в дальнейшей обработке эта часть не участвует. Элементы НЕ, на входах элементов И предотвращают формирование ложных сигналов ошибки для элементов а1, а2 и аа при появлении синдрома вида 111.

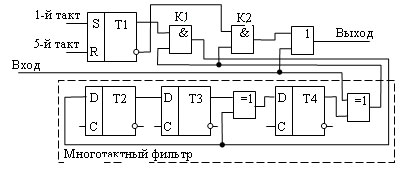

Принципиальная электрическая схема кодера циклического кода

Принципиальная электрическая схема кодера циклического кода (7,4) приведена на рисунке 7.

Кодер построен на многотактном фильтре (МФ) в качестве которого используется регистр. Количество D-триггеров в МФ соответствует степени порождающего полинома. Также в состав МФ входят логические элементы сложения по модулю два, их количество на один меньше ненулевых членов порождающего полинома. Данные элементы располагаются на месте нулевого члена порождающего полинома и после триггера соответствующего члену х0. В данной схеме МФ соответствует полиному G(x)=х3+х2+х0. Также в схему кодера входит два ключа в качестве которых используются логические элементы И, тактового RS-триггера и логического элемента ИЛИ.

Формирование кодовой комбинации на выходе схемы происходит за 7 тактов. За первые четыре такта на выход поступают информационные разряды: тактовые импульсы подаются на установочный вход единицы «S» RS-триггера, в результате чего открывается ключ К1 и входные информационные разряды через элемент ИЛИ поступают на выход. Одновременно информационные разряды поступают в МФ где осуществляется вычисление проверочных разрядов. С пятого по седьмой такты формируются проверочные разряды. При этом тактовые импульсы подаются на установочный вход нуля «R» RS-триггера. Ключ К1 закрывается а К2 открывается и проверочные разряды из МФ через К2 и элемент ИЛИ поступают на выход.

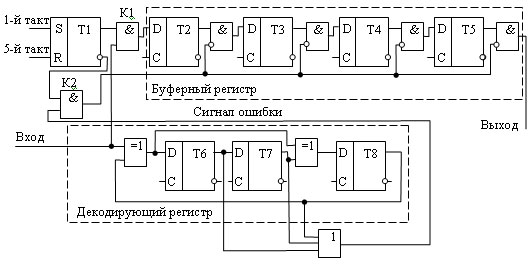

Принципиальная электрическая схема декодера циклического кода

Принципиальная электрическая схема декодера циклического кода (7,4) представлена на рисунке 8.

Данный декодер способен только обнаруживать ошибки и не способен их исправлять. В его состав входят так же как и в кодер тактовый RS-триггер, два ключа К1 и К2, элемент формирования ошибки ИЛИ и декодирующий регистр, принцип построения которого аналогичен построения МФ кодера. Кроме того устройство содержит буферный регистр состоящий из D-триггеров и логических элементов И у которых один из входов инверсный.

За первые четыре такта информационные разряды поступающей кодовой комбинации, через К1, записываются в буферный регистр: Тактовые импульсы поступают на установочный вход единицы «S» RS-триггера и К1 открывается. Одновременно разряды кодовой комбинации поступают в декодирующий регистр, где вычисляется синдром. Если синдром кода не равен нулю, то схема или формирует сигнал ошибки «1», который поступает на вход К2. За 5 -7 такты открывается К2 и закрывается К1. В случае ошибки на входе и выходе К2 действуют единицы, а следовательно логические элементы И в схеме буферного регистра закрыты и информация хранимая в регистре стирается. Если же комбинация принята верно, т. е. синдром равен нулю, то информационные разряды поступают на выход декодера и используются для дальнейшей обработки.

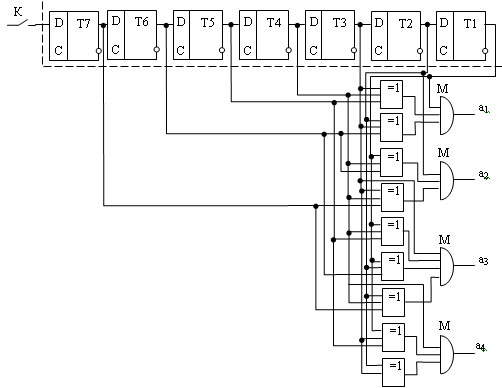

Принципиальная электрическая схема декодера мажоритарного циклического кода

Принципиальная электрическая схема декодера мажоритарного кода (7,3) представлена на рисунке 9.

Декодер включает в себя буферный регистр и схему вычисления линейных выражений. Количество ячеек буферного регистра соответствует разрядности кодовой комбинации Bip(x). Схема вычисления линейных выражений содержит логические элементы сложения по модулю два и мажоритарные элементы (М). Количество логических элементов соответствует количеству линейных выражений кода, а количество мажоритарных элементов соответствует разрядности информационной части комбинации, т. е. разрядности Ai(x).

В начале цикла вся кодовая комбинация Bip(x)’ через ключ (К) записывается в ячейки буферного регистра, причем, старший разряд а1’ записывается в триггер Т1, а2’ в Т2, а3’ в Т3, а4’ в Т4, b1’ в Т5, b2’ в Т6, b3’ в Т7. Затем ключ размыкается и происходит вычисление линейных выражений для всех информационных символов. Результаты вычисления поступают в мажоритарные элементы. Кроме этих выражений в соответствующие мажоритарные элементы поступают символы тех разрядов, для которых определяются линейные выражения. Мажоритарные элементы выносят решения о принятых символах аi. Затем информационная комбинация Аi(х) поступает на выход декодера.